情報処理技術者試験対策のページ>午前対策 目次

テクノロジ系 コンピュータシステム ハードウェア

ハードウェア

- 電気・電子回路

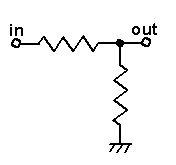

- PWM(パルス幅変調)で変調された信号をアナログ電圧に変換する回路

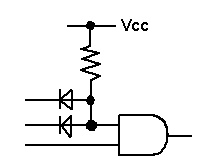

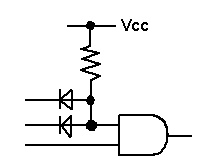

- TTLレベルの2入力AND回路を3入力AND回路にするために、入力部に回路を追加した3入力AND回路

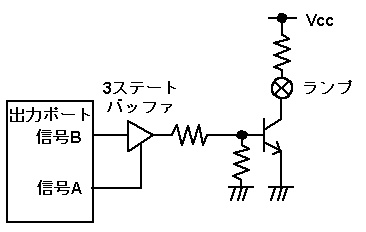

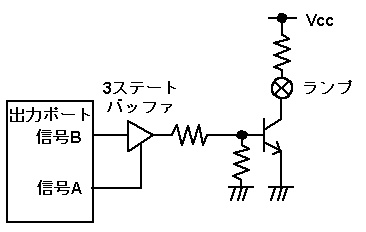

- マイコンの出力ポートに接続されたランプが点灯するランプ回路

信号A High

信号B High

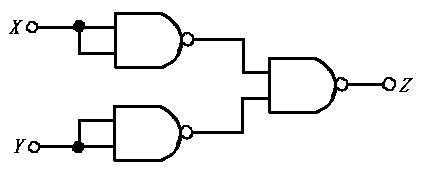

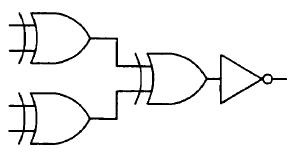

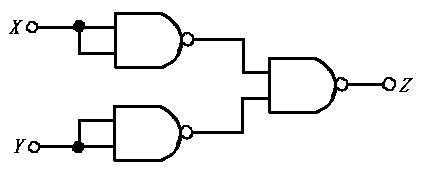

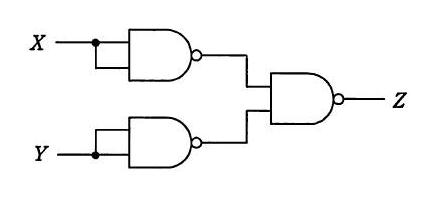

- NAND素子を用いた組合せ回路

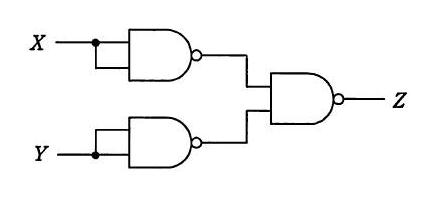

Z=X+Y

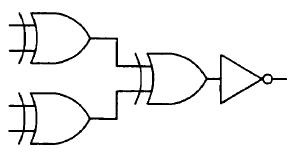

- 4ビットの入力データに対し、1の入力数が0個又は偶数個のとき出力が1に、奇数個の時出力が0になる回路

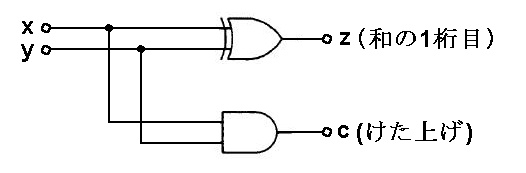

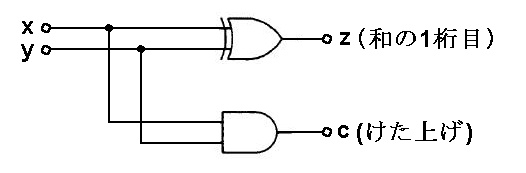

- 半加算器

xとyは1けたの2進数

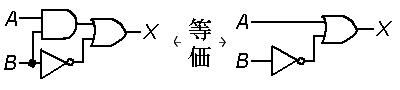

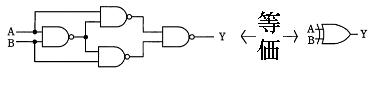

- 等価回路の例

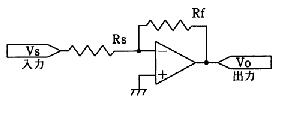

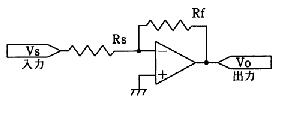

- 反転増幅器

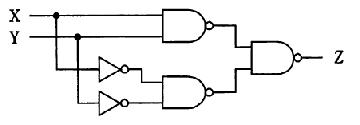

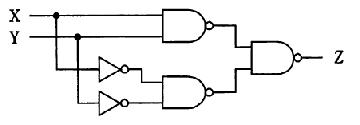

- 入力XとYの値が同じ時にだけ、出力Zに1を出力する回路

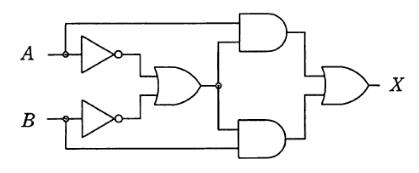

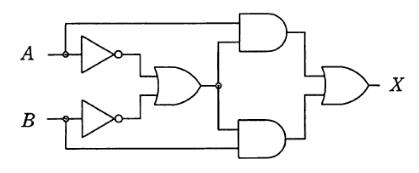

- 回路の例

- X = a・b

+ a・b

- Z=X+Y

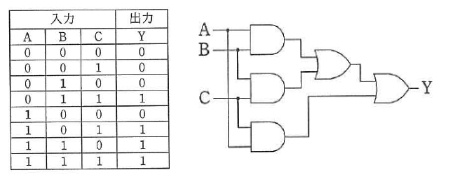

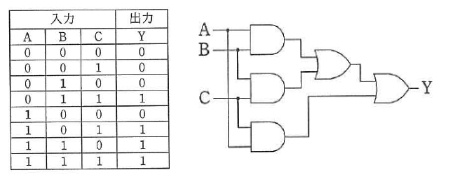

- 3入力多数決回路

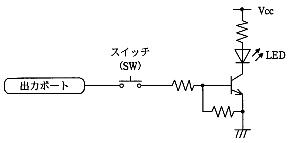

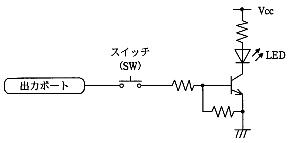

- LED点灯回路の動作

SWオフ:消灯

SWon+出力ポートHigh:点灯

SWon+出力ポートLow:消灯

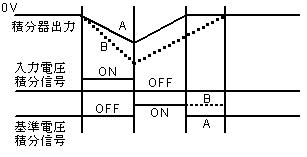

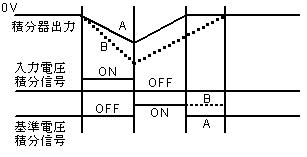

- 二重積分方式のA/D変換器によるA/D変換の信号波形

波形B(破線)と比べた波形A(実線)を示す状態

A/D変換器への入力電圧:低い

逆積分時間:短い

ディジタル値出力:小さい

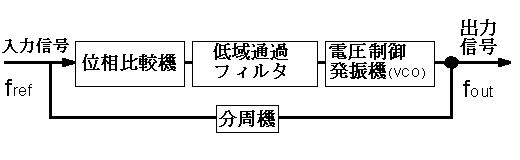

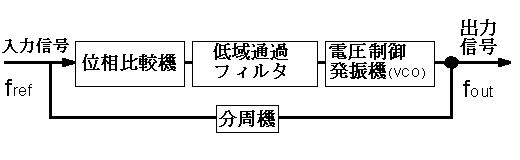

- PLLのブロック図

PLLがロック状態で、分周器の分周比がNの場合(1/N分周機を使用)、出力周波数foutを基準周波数frefで表すとNfref

- 機械・制御

- ファームウェア

-

ハードウエアに組み込まれた制御用のソフトウエア

-

LSIなどに書き込まれた状態でハードウェアに組み込まれている

- シーケンス制御

産業機器の機器制御に使われる制御方法で、あらかじめ定められた順序又は条件に従って、制御の各段階を逐次薦めていく制御方法

- PLC ( Programmable Logic Controller )

- 電力線に情報信号を載せて通信する技術

-

産業機器の機械制御装置として使われる

-

主としてラダー図を使ったシーケンスプログラムによって制御する

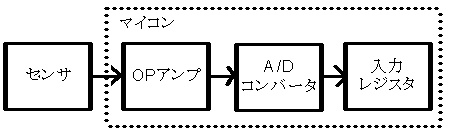

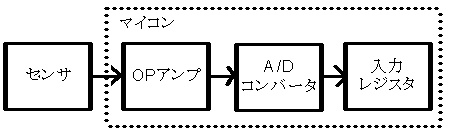

- センサが出力するアナログ電圧をマイコンに取り込むための構成

- チャタリング

-

機械式接点の押しボタンスイッチを1回押すことに対して、押してから数ミリ秒の間、複数回のON、OFFが発生する現象

- スイッチのチャタリングを除去する方法

- RSフリップフロップでスイッチ信号を受ける

スイッチの変化を最も遅延が少なく読み込め、高速

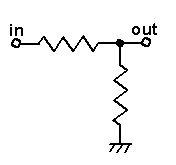

- CR積分回路でスイッチ信号を受け、シュミットトリガ回路で整形する

キャパシタに電荷が溜るまでの時間がかかる

- スイッチが接続された入力ポートの値を2回読み込んで判定する

ソフトウェアを使って実現するため、非常に時間がかかる

- ディジタルフィルタで振動性分だけを除去する

高性能なノイズ除去が可能だが、それほど速度は出ない

- A/D変換

サンプリング周期が短いほど、高い周波数の信号まで変換できる

- DCモータにおけるPWM制御方法

パルスのデューティー比によって、モータの回転数を制御する

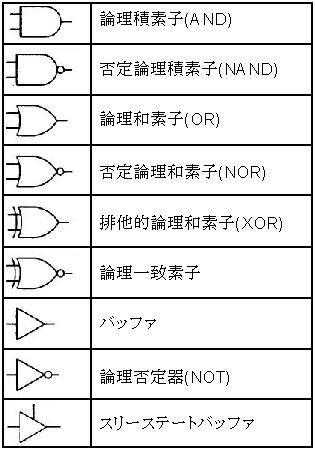

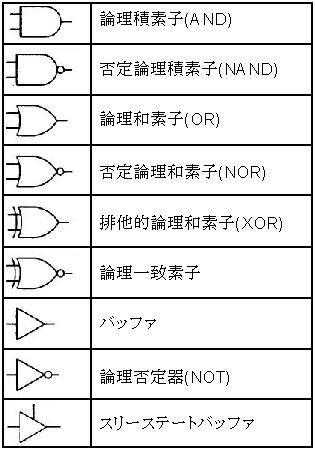

- 論理設計

- ASIC設計におけるトップダウン設計

抽象度の高い動作レベルでの記述や、RTL(レジスタトランスファレベル)での記述を用いて設計する

- 構成部品及び要素と実装

- ディジタルシグナルプロセッサ ( DSP ; Digital Signal Processor )の特徴

積和演算、浮動小数点演算などの機能を内蔵しているので、ディジタルフィルタを実現するのに適している

- インサーキットエミュレータ

MPUの代わりとしてボードに接続し、ソフトウェアやハードウェアのデバッグを行う

- 組込みシステムで使用されるI^2Cバスの特徴

クロックとデータの2線式バスである

- シングルチップマイコンの特徴

入出力機能が内蔵されている

- ラッチ回路

1ビットの情報を保持するため電子回路

NAMD回路を2個組み合わせて、互いに相手の出力を入力に戻す

- フリップフロップ

二つの安定状態を持つ回路で、SRAMの記憶セルに使用される順序回路の基本構成要素

- システムLSI

複数のLSIで実現していた機能を1チップに集約したもの

- ワンチップマイコン

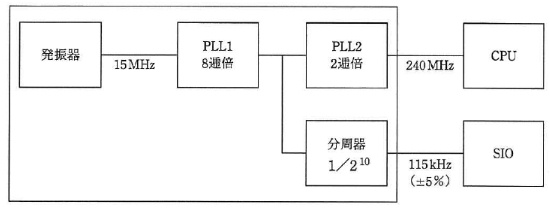

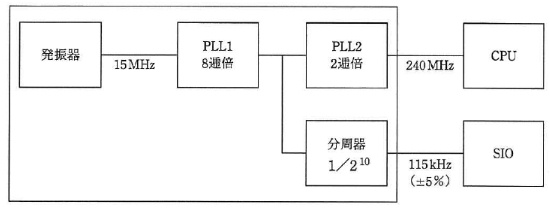

- ワンチップマイコンにおける内部クロック発生器のブロック図

15MHzの発信機と、内部のPLL1、PLL2及び分周期の組合せでCPUに240MHz、

シリアル通信(SIO)に115kHzのクロック信号を供給する(シリアル通信のクロック精度は±5%以内)

- 内蔵メモリとしてフラッシュメモリが採用されている理由

マイコン出荷後もソフトウェアの書換えが可能である

- SoC ( System On a Chip )

- 必要とされるすべての機能(システム)を同一プロセスで集積した半導体チップ

- 従来はボード上で実現していたシステムを、一つのチップ上で実現したLSIのこと

- 半導体素子

- LSIの故障メカニズムの一つであるESD ( Electrostatoc Discharge )破壊

静電気放電によって、半導体素子が破壊されてしまう現象

- クロックジェネレータ

- PC又は組込み機器のクロックジェネレータにSSCG(Spread Spectrum Clock Generator)が用いられることがある。この効果

クロックからの放射ノイズの影響を低減する

- マイクロホンから入力された音声信号をメモリに記録する機能と、メモリに記録された音声データをスピーカから出力する機能とを持つディジタル録音・再生システム

A/D変換器の出力及びD/A変換器の入力を、メモリのデータ線に接続する

- フィールドプログラマブルロジック

基本論理回路で構成された論理モジュールをチップに配置し、ユーザがSRAMなどに配線情報を記憶させる

- 半導体素子

- 素子一覧

- システムLSI

- SoC(System on a Chip)

- FPGA

- MEMS

- 診断プログラム

- 消費電力

組込みシステム・組込みソフトウェア

- 組込みシステムの特徴

組込みシステムは専用化されたハードウェアやソフトウェアから成る

- 制御系の組込みシステムで使用されるリアルタイムOS

タスク生成は主に静的に行う

- エンジン制御、ハードディスク制御などの制御系ハードリアルタイムシステムでリアルタイムOSを活用する理由

定められた時間内にイベントに対応した処理を完了させる機構が必要だから

- 用途

- 適切

- FA機器又は器量機器を制御するシステム

- 音響・映像機器を制御するシステム

- 銀行のATM端末システム

- 不適切

- 組込みソフトウェアの例

自動車のエンジンに供給する燃料の量を制御するソフトウェア

- 組込みシステムの特許におけるライセンス

新規開発した組込み製品のハードウェア部分だけが、他者の特許に抵触している場合、その部分のライセンスを得ないと権利侵害になる

- リアルタイム性

定められた時間の範囲内で一定の処理を完了する性質

- 組込みシステムでリアルタイムOSがもちいられる理由

期待される応答時間内にタスクや割込みを処理するための仕組みが提供される

- 多重にハードウェア割込みが発生する組込みシステムにおけるIRS

( Interrupt Service Routine ) の処理

低い優先度の割り込みによるISR処理中に割込み禁止を行うと、その間に発生した高い優先度の割込みに対するISR応答時間は長くなる

- 組込みシステムにおけるリアルタイムシステムにおいて、システムへの入力に対する応答

定められた制限時間内に応答する

- リアルタイムOSにおけるコンテキストの使用方法

割込み処理を、割込み処理ごとのコンテキストで実行させる

- マイコンのJTAGを利用したデバッガ

マイコン自身にデバッグに必要となる機能が内蔵されており、それを外部から制御するための端子がある。子の端子を利用してデバッグを行う

- 組込みシステムにおけるコデザイン

上流工程段階で、ハードウェアとソフトウェアの機能分担を強調シミュレーションによって十分検証することで、仕様を満たしていることを確認していく手法

- 従来型設計

ハードウェアとソフトウェアとの開発を独立に並行して行った後、両者を組み合わせて統合テストを行うことで、初めて仕様を満たしているかどうかの検証を行う手法

- リアルタイムOSにおけるコンテキストの使用方法に関する記述

割込み処理を、割込み処理ごとのコンテキストで実行させる

- 組込みシステムでリアルタイムOSが用いられる理由

期待される応答時間内にタスクや割込みを処理するための仕組みが提供される

- 組込みシステムのプログラムを格納するメモリとして、マスクROMを使用するメリット

出荷後のプログラムの不正な書換えを防ぐことができる

- 電化製品などに組込みシステムを採用する利点

製品の改良にあたって、ソフトウェアの変更だけで一定範囲の機能追加が可能となる

- 多重割込みを処理するリアルタイムOSの割込みハンドラ処理

割込み禁止状態での処理を極力減らして、割込み可能状態で動作する

- MDA

組込みソフトウェアなどの設計にも有効な技法であって、システムをプラットフォームに依存する部分と依存しない部分とに分けてモデル化することを特徴とする技法